1. Jurnal [Kembali]

Gerbang logika AND adalah gerbang logika yang membutuhkan

dua atau lebih masukan (input) untuk menghasilkan satu output. Ketika salah

satu atau seluruh bilangan biner pada inputnya adalah 0 maka output yang akan

dihasilkan juga 0. Sedangkan jika inputnya adalah 1 seluruhnya, maka outputnya

adalah 1. dilihat bahwa pada gerbang AND,

keluarannya akan bernilai 1 jika semua input adalah 1. Dan jika salah satu

atau lebih input ada yang bernilai nol maka ouput akan bernilai nol.

Untuk gerbang AND memakai prinsip perkalian.

Gerbang NOT merupakan gerbang di maan keluarannya akan selalu berlawanan dengan masukannya. Bila pada masukan diberikan tegangan, maka transistor akan jenuh dan keluaran bertegangan nol. Sedangkan bila pada masukannya diberi tegangan tertentu, maka transistor akan cut off, sehingga keluaran akan bertegangan tidak nol.

Gerbang NOT merupakan gerbang di maan keluarannya akan selalu berlawanan dengan masukannya. Bila pada masukan diberikan tegangan, maka transistor akan jenuh dan keluaran bertegangan nol. Sedangkan bila pada masukannya diberi tegangan tertentu, maka transistor akan cut off, sehingga keluaran akan bertegangan tidak nol. |

| Tabel Kebenaran Logika NOT |

3. Rangkaian Simulasi [Kembali]

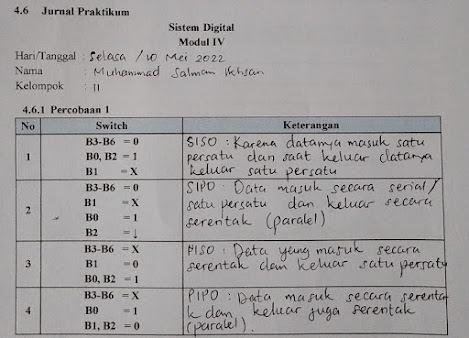

Pada rangkaian ini memiliki 4 input masukan dari J-K flip flop dan 4 input keluaran dari J-K flip flop dimana akan terjadi proses operasi SISO, SIPO, PISO, dan PIPO pada rangkaian sesuai pengaturan switch dan kondisi.Maka padaprosesnya akan terjadi sistem kerja serial dan paralel yang dimana pada rangkaian akan terjadi perwakilan dari penggeseran pada sistem serial maupun serempak pada sistem paralel baik itu masukan maupun keluaran suatu biner yang dimana pergeseran maupun serempak pada sistem serial dan paralel ini akan mewakili MSB dan LSB dari 4 bit binner masukan dan keluaran. Terjadinyam proses input dan output logika pada rangkaian ini juga berarti bahwa proses terjadinya register geser ini dapat menyimpan memori sementara pada masukan menuju keluaran bit ke-4 dari dearah lingkup keluaran 4 bit.

Kesimpulan dari percobaan 1, maka didapatkan hasil output pada masing-masing kondisi pada jurnal, untuk kondisi 1 bersifat SISO, karena inputan dan keluarannya mengalami pergeseran serta masuk dan keluar secara bergantian (satu per satu/serial). Untuk kondisi 2 bersifat SIPO, karena inputannya masuk secara bergantian (satu per satu/serial), sedangkan untuk keluarannya keluar secara serentak (paralel). Untuk kondisi 3 bersifat PISO, karena inputannya masuk secara serentak (paralel), sedangkan keluarannya keluar secara bergantiang (satu per satu/serial). Dan untuk kondisi 4 bersifat PIPO, karena inputan dan keluarannya masuk secara bersamaan (serentak/paralel).

6. Analisa [Kembali]

Jawab :

7. Link Download [Kembali]

Tidak ada komentar:

Posting Komentar