7.6 : Carry Propagation–Look-Ahead Carry Generator

1. Tujuan

[Kembali]- Untuk menyelesaikan tugas Sistem Digital

- Untuk memahami materi 7.6 Carry propagation

1) Encoder 74LS147

2) Decoder 4511

Decoder merupakan sebuah alat yang dimanfaatkan untuk mengembalikan sebuah proses decoding sehingga membuat kita bisa menerima informasi yang asli.

3) Gerbang NOT

Disebut juga sebagai Inverter (pembalik), Gerbang NOT memang memiliki konfigurasi terbalik. Ia dapat mengubah input 0 menjadi output 1, sedangkan input 0 akan menjadi output 1. Gerbang NOT juga sangat berbeda dengan gerbang lainnya, karena ia hanya mempunyai 1 input dan 1 output saja.

4) Logic State

| Feature | Input 1A Input 2A output A Input lB Input 2B output B . . B I u I vc~ Input ID Input 2D output . |

5) 7 Segment

Layar tujuh segmen adalah salah satu perangkat layar untuk menampilkan sistem angka desimal yang merupakan alternatif dari layar dot-matrix. Layar tujuh segmen ini sering kali digunakan pada jam digital, meteran elektronik, dan perangkat elektronik lainnya yang menampilkan informasi numerik.

Penambah biner empat-bit yang dijelaskan di halaman sebelumnya dapat digunakan untuk menambahkan dua biner empat-bit angka. Beberapa nomor penambah tersebut digunakan untuk melakukan operasi penambahan pada biner bit yang lebih besar angka. Masing-masing penambah terdiri dari empat penambah penuh (FA) yang terhubung dalam kaskade. blok pengaturan skema penambah empat-bit direproduksi pada Gambar. 7.30(a) untuk referensi dan selanjutnya diskusi. Jenis penambah ini juga disebut penambah biner paralel karena semua bit dari augend dan addend hadir dan diumpankan ke blok adder penuh secara bersamaan. Secara teoritis, penambahan operasi di berbagai penambah penuh berlangsung secara bersamaan. Apa yang penting dan menarik bagi pengguna, terlebih lagi ketika mereka menggunakan sejumlah besar penambah seperti itu dalam sistem perhitungan mereka secara keseluruhan, adalah apakah hasil penambahan dan pelaksanaan tersedia bagi mereka pada saat yang bersamaan. Dengan kata lain, kita perlu melihat apakah operasi penambahan ini benar-benar paralel. Kita akan segera melihat bahwa tidak demikian. ada di fakta dibatasi oleh apa yang dikenal sebagai waktu propagasi carry. Lihat Gambar 7.30(a) dan (b). Gambar 7.30(b) menunjukkan diagram logika dari penambah penuh. Di sini, Ci dan Ci+1 adalah input dan output CARRY; Pi dan Gi adalah dua variabel biner baru yang disebut CARRY PROPAGATE dan CARRY GENERATE dan akan menjadi ditangani sedikit kemudian Untuk i=1, diagram pada Gambar 7.30(b) adalah diagram penambah penuh LSB dari Gambar 7.30(a). Kita bisa melihat di sini bahwa C2, yang merupakan keluaran CARRY dari FA (1) dan masukan CARRY untuk FA (2), akan muncul pada keluaran setelah minimum dua penundaan gerbang ditambah penundaan karena penambah setengah setelah penerapan input Ai, Bi dan Ci

Keadaan tunak C2 akan tertunda oleh dua penundaan gerbang setelah munculnya C1. Demikian pula, C3 dan C4kondisi tunak akan menjadi empat dan enam penundaan gerbang masing-masing setelah C1. Dan carry terakhir C5 akan muncul setelah pukul delapan keterlambatan gerbang.

Memperluasnya sedikit lebih jauh, mari kita asumsikan bahwa kita memiliki pengaturan kaskade dua empat-bit penambah untuk dapat menangani angka delapan bit. Sekarang, C5 akan membentuk input CARRY ke yang kedua penambah empat bit. Keluaran akhir CARRY C9 sekarang akan muncul setelah 16 kali penundaan gerbang. propagasi carry ini delay membatasi kecepatan penambahan dua angka. Output dari pengaturan penambah seperti itu akan benar hanya jika sinyal diberikan waktu yang cukup untuk merambat melalui gerbang yang terhubung antara masukan dan keluaran. Karena pengurangan juga merupakan proses penjumlahan dan operasi seperti perkalian dan pembagian juga merupakan proses yang melibatkan penambahan dan pengurangan berturut-turut, waktu yang dibutuhkan oleh penambahan proses sangat kritis. Salah satu metode yang mungkin untuk mengurangi waktu tunda propagasi carry adalah dengan menggunakan gerbang logika yang lebih cepat.

Tetapi kemudian ada batas di bawahnya penundaan gerbang tidak dapat dikurangi. Ada teknik terkait perangkat keras lainnya, yang paling banyak digunakan di antaranya adalah konsep look-ahead carry. Konsep ini mencoba untuk melihat ke depan dan menghasilkan carry untuk operasi penambahan tertentu yang akan sebaliknya telah dihasilkan dari beberapa operasi sebelumnya. Untuk menjelaskan konsepnya, mari kita definisikan dua variabel biner baru: Pi disebut CARRY PROPAGATE dan Gi disebut CARRY GENERATE. Variabel biner Gi disebut demikian karena menghasilkan carry setiap kali Ai dan Bi bernilai '1'. Variabel binerPi disebut CARRY PROPAGATE karena berperan dalam propagasi Ci ke Ci+1. MEMBAWA, SUM, CARRY GENERATE dan CARRY PROPAGATE parameter diberikan sebagai berikut:

ekspresi:

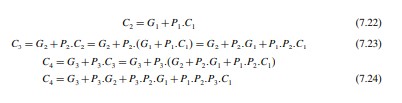

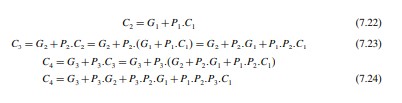

Pada langkah berikutnya, kami menulis ekspresi Boolean untuk output CARRY dari setiap tahap penambah penuh di penambah biner empat bit. Kami memperoleh ekspresi berikut:

Dari ekspresi untuk C2, C3 dan C4 jelas bahwa C4 tidak perlu menunggu C3 dan C2 untuk menyebar. Demikian pula, C3 tidak menunggu C2 untuk menyebar. Implementasi perangkat keras dari ekspresi ini memberikan kami semacam genset gendongan lihat-depan. Generator carry lihat ke depan yang mengimplementasikan hal di atas ekspresi menggunakan logika AND-OR ditunjukkan pada Gambar 7.31. Gambar 7.32 menunjukkan adder empat bit dengan konsep look-ahead carry yang tergabung. blok generator pembawa lihat-depan berlabel mirip dengan yang ditunjukkan pada Gambar. 7.31. Gerbang logika yang ditunjukkan pada kiri blok mewakili bagian setengah penambah input dari berbagai penambah penuh yang membentuk empat bit penambah Gerbang EX-OR yang ditunjukkan di sebelah kanan adalah bagian dari output setengah penambah dari berbagai penuh

penambah.

Semua jumlah keluaran dalam kasus ini akan tersedia pada keluaran setelah penundaan dua tingkat logika gerbang. 74182 adalah IC generator carry look-ahead yang khas dari keluarga logika TTL. IC ini dapat digunakan untuk menghasilkan input carry yang relevan untuk empat penambah biner empat-bit yang terhubung dalam kaskade untuk melakukan operasi pada dua nomor 16-bit. Tentu saja, penambah empat bit harus dari jenis yang dapat menghasilkan CARRY GENERATE dan CARRY PROPAGATE output. Gambar 7.33 menunjukkan susunannya. Di dalam gambar yang ditunjukkan, Cn adalah input CARRY, G0, G1, G2 dan G3 adalah input CARRY GENERATE untuk 74182 dan P0, P1, P2 dan P3 adalah input CARRY PROPAGATE untuk 74182. Cn+x, Cn+y dan Cn+z adalah keluaran CARRY yang dihasilkan oleh 74182 untuk penambah empat bit. Keluaran G dan P dari 74182 perlu mengalir. Gambar 7.34 menunjukkan pengaturan yang diperlukan untuk menambahkan dua 64-bit angka.

Prosedur percobaan :

1. Bukalah aplikasi proteus terlebih dahulu.

2.Buka schematic capture, pilih bagian component mode ( ), dan pada bagian devices klik 'P'.

), dan pada bagian devices klik 'P'.

3.Pastikan kategorinya berada pada all categories agar mudah dalam melakukan pencarian.

4.Ketikkan semua nama bahan komponen yang dibutuhkan dalam rangkaian.

5.Double klik komponen yang kita butuhkan agar komponen tersebut muncul dikolom Devices.

6. Buka bagian Terminals mode ( ).

).

7.Pilih terminal yang diperlukan.

8.Setelah semua komponen didapatkan, letakkan komponen pada papan rangkaian.

9.Rangkailah semua komponen sesuai prinsipnya.

10.Klik play (  ) pada bagian kiri bawah aplikasi untuk menjalankan rangkaian simulasi.

) pada bagian kiri bawah aplikasi untuk menjalankan rangkaian simulasi.

11.Saat di play, jika rangkaian simulasi sudah benar dan sesuai, maka akan muncul output.

Prinsip Kerja

![]() ), dan pada bagian devices klik 'P'.

), dan pada bagian devices klik 'P'.![]() ).

).![]() ) pada bagian kiri bawah aplikasi untuk menjalankan rangkaian simulasi.

) pada bagian kiri bawah aplikasi untuk menjalankan rangkaian simulasi.

Tidak ada komentar:

Posting Komentar